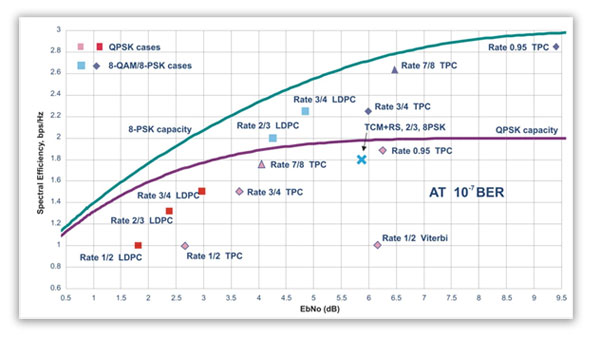

Low-Density Parity-Check Codes enable near Shannon limit performance. LDPCs were originally proposed in 1962, but only recently regained attention. LDPCs are coded according to sparse parity-check matrixes and decoded using iterative algorithms similar to that of turbo decoding. Based on recent research, LDPCs were found to have the potential to offer both better performance and lower decoding complexity in many cases. In fact, an irregular rate R=1/2 LDPC with block length of 107 currently holds the record of best FEC performance, 0.04 dB to the Shannon limit at BER level of 10-6 in an AWGN channel. The chart below illustrates the relative performance of LDPC:

LDPC has also been accepted as part of the DVB-S2 specification. We developed the LDPC encoder and decoder in conjunction with Comtech AHA in an FPGA package, and were the first to market with this technology in 2007.